通过大郭2021年10月22日

通过大郭2021年10月22日

半导体行业正在接近晶体管尺度与几十个原子。某些时候,摩尔定律,即微型芯片上的晶体管数量大约每两年就增加一倍,不可避免地必须停止。本文旨在介绍单电子阈值逻辑门作为一个可能的解决方案物理微型化的极限。

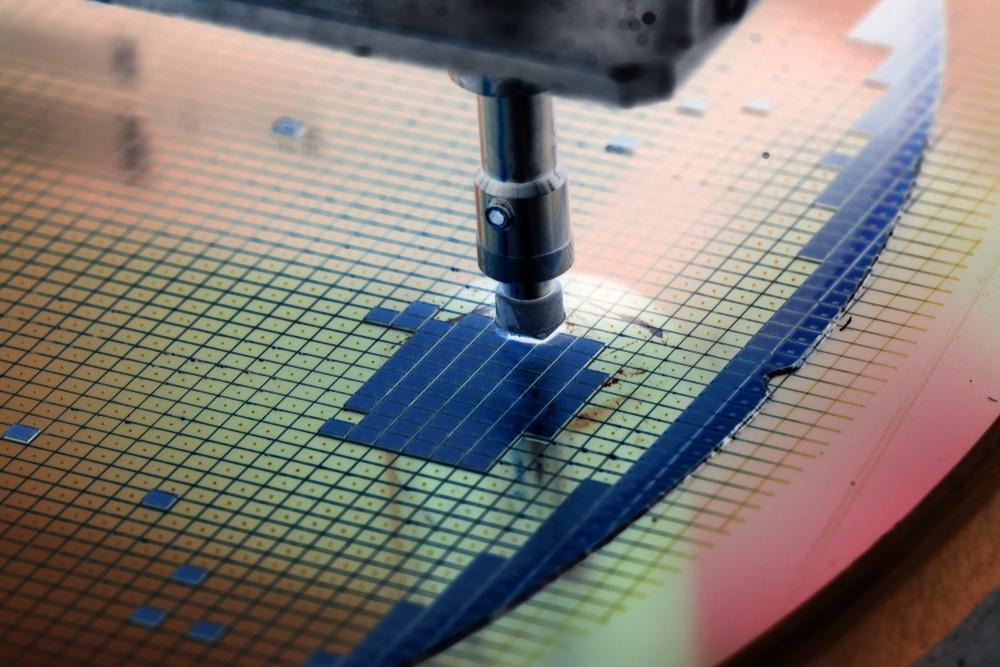

图片来源:Phaigraphic / Shutterstock.com

CMOS技术的局限性

互补金属氧化物半导体(CMOS)技术一直占据着固态电子行业近半个世纪。工程师在这个领域是用来处理怀疑技术的前景进一步小型化,十年后的十年里,他们已经能够克服障碍沿途的摩尔的律法,却这一次,它是不同的。

物理学的领域本身是变化的,传统的建模工具需要重新评估。最先进的商业晶体管目前门长度20至40 nm之间。理智的看待这个问题,硅本身的inter-atomic间距大约是0.5海里。

简而言之,晶体管在这个规模开始体验量子现象,导致偏离经典模型设计使用。一个具体的例子是这些晶体管在他们的国家开始体验“泄漏”随着晶体管的沟道,尽管各地的电子隧道势垒,使不受欢迎的功率损耗。

各向异性热导体解决电气部件过热

第二个限制CMOS,经常被忽视由于其成熟的低成本制造的基础设施,是天生的冗余以及与其关联的逻辑方案。

每个布尔函数实现,补充的晶体管网络相关的函数也必须实现,基本上翻倍电路的复杂性。年底CMOS打开一个解决这个问题的机会,和任何可以消除这种冗余的解决方案,在理论上,节省规模、成本、和力量。

单电子阈值逻辑的优点

目前大部分的研究主要集中在设计替代方案以CMOS逻辑。荷兰代尔夫特大学的研究人员提出,早在2001年,一个可能实现的一个基于单电子的阈值逻辑门操作。

简短的背景,目前主要是通过实现组合逻辑芯片电路组成,根据布尔代数规则,使用一组的基本逻辑门功能完成。

图片来源:宏观照片/ Shutterstock.com

这些基本盖茨包括,例如,与非,也和的集合,或者,而不是门。阈值逻辑的概念绕过了布尔代数操作的需要。相反,它把逻辑门的输出开关,打开如果输入的加权总和达到或超过一定的门阈值,如果否则仍掉。

在上述提议,单电子的说法来源于事实的开/关状态输出电压是由一个电子的隧穿和孤立金属小岛夹在电容连接。

这个概念逻辑门带来了许多优势和机遇。首先,这个设计将设备小型化的单电子性质的物理限制。此外,阈值逻辑能够模拟组合功能仅仅通过设置适当的输入权值。

这不仅避免了互补与CMOS晶体管网络,而且还消除了需要构造布尔盖茨对复杂组合逻辑电路。大幅减少冗余和电路等深度受益减少尺寸,功率和时间延迟。

为单电子设备未来的挑战

在实践中,nano-systems依靠量子现象非常敏感,使它们容易随机背景的指控。制作一个单电子设备在实验室并不是一件容易的事情,和实验数据仍然需要增加当前理论模型用于设备的设计。

除此之外,它是一个天生的签名的量子力学存在一个小规模和低能量之间的权衡。当前单电子设备必须运行在非常低的温度下,使这一技术挑战性的商业化。

最后,该行业的一个重大的挑战是设计一个具有成本效益的大规模生产的过程。CMOS目前拥有完善的基础设施,存在一个最小的经济动机所取代。然而,这最后一点可能很快就会改变在这个十年CMOS努力跟上摩尔定律,和半导体行业将被迫采取一个新的范式。

引用和进一步阅读

r . Cavin p Lugli诉Zhirnov, (2012)。欧洲杯线上买球科学与工程超越摩尔定律,页2 - 10,https://www.researchgate.net/publication/238594798_欧洲杯线上买球Science_and_Engineering_Beyond_Moore 's_Law

c . Lageweg s Cotofana, s . Vassilladis (2001)。线性阈值门在单电子技术实现VLSI IEEE计算机协会研讨会,页93 - 98。https://www.欧洲杯线上买球sciencedirect.com/science/article/pii/S221201731300594X

s . Muroga阈值逻辑及其应用,威利父子公司,纽约,1971年。https://www.scirp.org/ (S (oyulxb452alnt1aej1nfow45)) /引用/ ReferencesPapers.aspx ? ReferenceID = 2138383

免责声明:这里的观点是作者表达他们的私人能力,不一定代表AZoM.com T /有限的观点AZoNetwork这个网站的所有者和经营者。这个声明的一部分条款和条件本网站的使用。