2009年11月29日

科学家们格拉斯哥大学该公司与来自爱丁堡、曼彻斯特、南安普顿和约克大学的同事合作,开发出了有助于微芯片设计者创造未来集成电路的技术。

作为耗资530万英镑的工程与物理科学研究理事会(EPSRC) esscience试点项目欧洲杯线上买球NanoCMOS的一部分,他们开发了模拟工具,利用网格计算来预测数十亿个纳米晶体管(每一个都有自己独特和不可预测的原子尺度变化)将如何在一个电路中运行。

模拟将有助于解决晶体管内部的“统计变异性”问题,这是互补金属氧化物半导体(CMOS)微芯片在未来纳米级技术世代中继续扩大规模的主要障碍。

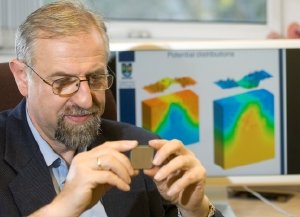

NanoCMOS的首席研究员Asen Asenov教授说:“纳米级晶体管是我们的电脑、手机、汽车、电视机和游戏机芯片的核心。它们在英国未来数字经济的愿景中发挥着至关重要的作用。

“自1947年硅晶片被发明以来,它们一直在变得越来越小,以至于今天我们可以在一小片硅晶片上放置数十亿个晶体管。”

今天的晶体管门长为40纳米;相比之下,人类的头发大约有10万纳米宽。然而,他们变得越小,原子规模的不完美和变化在每个晶体管成为一个问题。

晶体管之间的统计差异主要是由于离散掺杂剂的数量和位置的随机性造成的。离散掺杂剂是在硅中加入的化学香料,微芯片是由硅制成的,构成了单个晶体管的结构。

这种统计上的可变性意味着,尽管以相同的方式制造,但由数十亿具有各自独特特性的晶体管组成的电路,其性能可能不如预期的好。

Asenov教授表示:“如果我们要继续缩小晶体管的尺寸,以开发出更强大的电路,我们就需要从根本上采用新的方法来设计电路和系统,能够考虑到统计上的可变性。”

“到目前为止,摩尔定律一直是驱动芯片制造和设计行业的动力。摩尔定律是1965年由英特尔联合创始人戈登·摩尔提出的,他预测晶体管的尺寸将不断扩大,可以放置在微芯片上的晶体管的数量将每两年翻一番。但‘快乐的伸缩’时代已经结束了。”

然而,Asen Asenov教授和他的团队已经与领先的设计公司、芯片制造商和软件供应商合作,应用网格计算技术来解决这个问题。

利用网格计算技术,在网络计算机集群上的数千个微处理器上进行了大量微观上不同的纳米晶体管的模拟,这些微处理器在一周内消耗了超过20年的CPU时间。因此,该研究小组首次能够准确预测,使用三维数值模拟,数十亿微观上不同的晶体管将如何在未来的计算机芯片上运行。

3D模拟为科学家提供了关于晶体管特性统计分布的信息,有助于预测硅片中有多少个晶体管可以工作。这些信息使得芯片设计者可以用可变和不可靠的晶体管设计出可靠的芯片。

对数量空前的晶体管的模拟结果将于12月在巴尔的摩举行的国际电子器件会议上公布。互补的结果也发表在领先的电子器件杂志《IEEE电子器件学报》的10月版上。

Asenov教授补充说:“NanoCMOS项目不仅帮助我们首次理解了统计变化的详细信息,还帮助我们开发了改进的算法,能够在大大减少计算工作量的情况下准确预测统计变化。”

“这将是一个巨大的好处,不仅对世界各地的主要半导体制造商,而且对充满活力的英国芯片设计行业,正面临现代纳米cmos技术和设计日益增加的挑战。”

NanoCMS网格计算技术是由格拉斯哥大学和爱丁堡大学的国家电子科学中心和曼彻斯特大学的西北电子科学中心开发的。欧洲杯线上买球