2013年1月3

几乎所有的计算机芯片都使用两种类型的晶体管:一种是p型晶体管,代表正极;另一种是n型晶体管,代表负极。提高芯片的整体性能需要在这两方面进行并行改进。

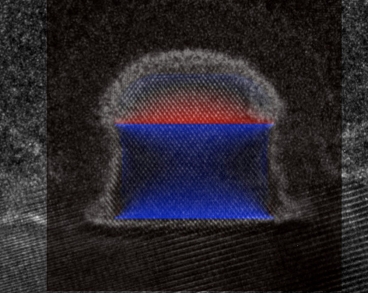

在这张实验晶体管的显微图中,蓝色高亮显示的是“应变”区域,锗原子被迫靠得比他们觉得舒服的地方更近。晶体管创纪录性能的原因之一是横向应变被放松了。图片来源:Winston Chern和James Teherani

在这张实验晶体管的显微图中,蓝色高亮显示的是“应变”区域,锗原子被迫靠得比他们觉得舒服的地方更近。晶体管创纪录性能的原因之一是横向应变被放松了。图片来源:Winston Chern和James Teherani

在12月的IEEE国际电子器件会议(IEDM)上,来自麻省理工学院微系统技术实验室(MTL)的研究人员展示了一种p型晶体管,其“载流子迁移率”是迄今为止测量到的最高的。按照这个标准,该器件的速度是之前实验用p型晶体管的两倍,几乎是商用p型晶体管的四倍。

像其他实验性的高性能晶体管一样,这种新器件的速度来自于它使用的非硅材料:在本例中是锗。在商业芯片中已经发现了锗合金,所以锗晶体管比用更奇特的材料制成的晶体管更容易集成到现有的芯片制造过程中。欧洲杯足球竞彩

这种新型晶体管还采用了所谓的三角设计,它可以解决一些困扰极小尺寸计算机电路的问题(英特尔已经在其最先进的芯片生产线中引入了这个问题)。由于所有这些原因,这种新设备为微芯片行业提供了一条诱人的前进道路——它可以帮助维持计算能力的快速增长,即消费者所期待的摩尔定律。

利弊

晶体管基本上就是一个开关:在一个位置上,它允许带电粒子通过;欧洲杯猜球平台在另一个位置,它没有。在n型晶体管中,粒子或载流子是电子,它们的流动产生普通的电流欧洲杯猜球平台。

另一方面,在p型晶体管中,载流子是带正电的“空穴”。p型半导体没有足够的电子来平衡原子的正电荷;当电子在原子之间来回跳跃,徒劳地试图保持它们的电平衡时,空穴在半导体中流动,就像波在局部来回移动非常小距离的水分子之间传播一样。

“载流子迁移率”测量的是载流子——无论是正电还是负电——在电场存在下移动的速度。增加的移动性可以转化为晶体管在固定电压下更快的开关速度,或在相同的开关速度下更低的电压。

几十年来,计算机芯片中的每个逻辑元件都由互补的n型和p型晶体管组成,它们巧妙的排列大大降低了芯片的功耗。总的来说,n型晶体管的载流子迁移率更容易提高;MTL研究人员的新装置证明p型晶体管应该能够跟上。

处理压力

电子工程和计算机科学教授朱迪·霍伊特(Judy Hoyt);欧洲杯线上买球她的研究生温斯顿·陈(新论文的主要作者)和詹姆斯·t·德黑兰尼;Pouya Hashemi,他当时是麻省理工的博士后,现在在IBM工作;Dimitri Antoniadis, Ray and Maria Stata电气工程教授;麻省理工学院和英属哥伦比亚大学的同事们通过“拉伸”晶体管中的锗原子,使其原子之间的距离比他们通常认为的更近,从而实现了创纪录的空穴迁移率。为了做到这一点,他们在几层不同的硅和硅锗复合材料上培育锗。锗原子自然地试图与它们下面的原子对齐,从而将它们压缩在一起。

霍伊特说:“这是我们必须要做的一套独特的材料结构,实际上是在MTL中制造的。”“这使我们能够在极限下探索这些材料。欧洲杯足球竞彩现在你买不到。”

“这些高应变层想要断裂,”Teherani补充道。“我们特别成功地培育了这些高应变层,并保持它们的应变没有缺陷。”事实上,霍伊特是应变硅晶体管的先驱之一,这种技术如今几乎在所有的商用计算机芯片中都能找到。在去年的IEDM上,她和麻省理工学院材料科学与工程Flemings-SMA教授尤金·菲茨杰拉德(Eugene Fitzgerald)因对固体器件和技术的杰出欧洲杯足球竞彩贡献获欧洲杯线上买球得了IEEE的安德鲁·s·格罗夫奖(Andrew S. Grove Award)。获奖声明提到霍伊特“在应变硅半导体材料方面的开创性贡献”。欧洲杯足球竞彩

守门

新型晶体管的另一个关键方面是它的三角设计。如果晶体管是一个开关,按下开关意味着向晶体管的“门”施加电荷。在传统晶体管中,栅极位于“通道”的顶部,载流子通过“通道”流动。随着晶体管变得越来越小,它们的栅极也缩小了。但在更小的尺寸上,这种同步小型化不会起作用:栅极将变得太小,无法可靠地关闭晶体管。

在三角型设计中,沟道高出芯片表面,就像火车场院里的车厢。为了增加它的表面积,门被包裹在通道的三个暴露的侧面——因此术语“三角”。通过证明他们可以在三角晶体管中实现高空穴迁移率,霍伊特和她的团队也表明,他们的方法将在未来的芯片中仍然有用。

“锗部分有助于增加驱动电流,而三角部分有助于减少关闭状态下的泄漏,”斯坦福大学Rickey/Nielsen工程教授Krishna Saraswat说,他没有参与这项研究。“因此,这两者的结合将为下一代提供一种理想的晶体管。”

Saraswat认为,半导体行业已经在计划向锗电路方向发展。他说:“我们的选择是在没有任何性能增益的情况下扩大硅晶体管的规模——只是获得更高的封装密度——或者获得更高的封装密度和更好的性能。”“很明显,这个行业将追求高强度的锗。”

麻省理工学院的研究人员的工作得到了美国国防高级研究计划局和半导体研究公司的支持。

来源:http://www.mit.edu/