2013年1月22日至23日,在法国格勒诺布尔举行的欧洲3D TSV峰会上,imec,一家世界领先的纳米电子研究机构今天宣布,他们与Cadence Design Systems一起开发、实施和验证了一种自动3D Design for test (DFT)解决方案,用于测试逻辑上dram堆栈中的逻辑内存互连。基于Cadence的解决方案®遇到®测试技术在一个工业测试芯片上得到验证,该芯片包含一个逻辑芯片和一个兼容jedec的Wide-I/O移动DRAM。

Imec的3D包装扩展的宽频i /O DRAM

Imec的3D包装扩展的宽频i /O DRAM

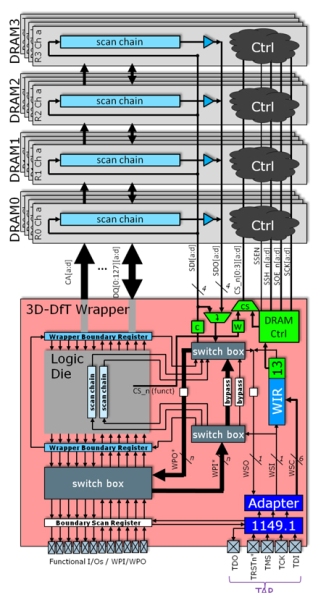

逻辑上内存3D堆栈提供了异构集成与高密度低功耗芯片间互连的可能性。因此,他们是首批将上市的3D产品之一,实现下一代高性能低功耗移动应用程序。最近,JEDEC发布了一个可堆叠的宽i /O移动动态随机访问存储器(dram)标准(JESD-229),指定了逻辑内存接口。与以前的许多dram不同,该标准包含边界扫描功能,以方便互连测试。Imec和Cadence现在提出了一种测试设计(DFT)体系结构和相应的自动测试模式生成(ATPG)方法。这是他们之前宣布的逻辑上的3D DFT架构的扩展,它支持逻辑芯片和堆叠在其上的DRAM之间互连的键后测试。

由Cadence和imec实现的解决方案包括在逻辑芯片中生成DRAM测试控制信号,并在3D测试体系结构的串行和并行测试访问机制(TAMs)中包含DRAM边界扫描寄存器。测试解决方案的自动化设计已在工业测试芯片上得到验证。测试芯片的设计是一个基于插入器的3D堆叠集成电路,包括一个硅插入器基模,一个40nm技术的94mm2逻辑片上系统,和一个单一的宽i /O DRAM级。验证结果表明,附加DFT包装器的硅面积与总逻辑模具尺寸(<0.03%)相比可以忽略不计。而且,测试模式生成非常高效(几十个模式,仅在几秒钟内生成)并且有效(100%覆盖目标错误)。使用Cadence Encounter RTL Compiler自动插入逻辑模中的所有3D-DFT逻辑,使用Encounter test ATPG生成互连测试模式。

Cadence公司的Encounter Test产品系列产品营销总监Bassilios Petrakis表示:“这种逻辑上内存的3D DFT解决方案是向面向下一代高性能、低功耗移动应用的3D叠加IC市场迈出的又一大步。“我们与imec的合作创造了一个行业领先的解决方案,为我们的客户提高了3D-IC设计的效率。”

“与Cadence的合作使我们能够在给定的设计中自动插入DFT电路,并自动生成互连测试模式。这种自动化流程使我们的技术对行业有价值。imec首席科学家Erik Jan Marinissen说:“我们有信心,我们也可以处理DFT特性,这些特性开始出现在其他3D存储标准中。”

部分工作已在ESiP项目中进行,该项目由ENIAC联合事业共同资助。