行业 - 首先成就进步分10nM技术节点

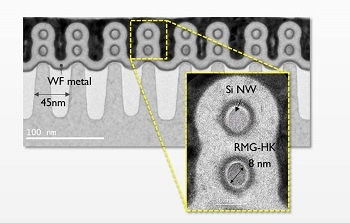

今天,在2016超大规模集成电路技术与电路研讨会上,纳米电子研究中心IMEC.提出了由直径仅为8纳米的垂直堆叠水平硅(Si)纳米线(NWs)构成的全栅(GAA) n-和p-MOSFET器件。该器件采用行业相关的替代金属栅(RMG)工艺在块硅基片上制作,具有优良的短沟道特性(SS = 65 mV/dec, DIBL = 42 mV/V, LG = 24 nm),性能水平可与finFET参考器件相媲美。

GAA器件结构提供最佳的静电控制,从而实现最终的CMOS器件缩放。此外,水平NWs是RMG finfet的自然延伸,而垂直NWs则需要更多的颠覆性技术变革。此外,NWs的叠加最大限度地提高了每个足迹的驱动电流。Imec成功地结合了这三个方面,并首次展示了按比例尺寸垂直堆叠的水平硅纳米线:直径为8纳米、横向间距为45纳米、垂直间距为20纳米。

与传统的散装FinFET流相比,IMEC在过程流动中实施了两个主要差异。首先,在750°C下致密化(STI)致密化,导致锐硅 - 锗(SiGe)/ Si界面,这对于良好控制的Si NW释放至关重要。其次,施加低复杂性接地平面掺杂方案,抑制底部寄生通道。

通过用固体静电控制展示堆叠的纳米线,在缩放尺寸下,并在散装硅基板上使用行业相关的RMG工艺,IMEC实现了可以为实现Sub-10nm技术节点铺平道路的突破性结果。即将到来的研究阶段将侧重于实现更密集的音高,并利用这些知识来开发门 - 全面横向纳米线CMOS器件。

Dan Mocuta,Director Logic Device和IMEC集成

IMEC对高级逻辑缩放的研究是与IMEC的核心CMOS计划合作进行的,包括GlobalFoundries,Intel,Micron,SK Hynix,三星,台积电,华为,高通和索尼。